ก้าวใหม่ของหน่วยความจำ

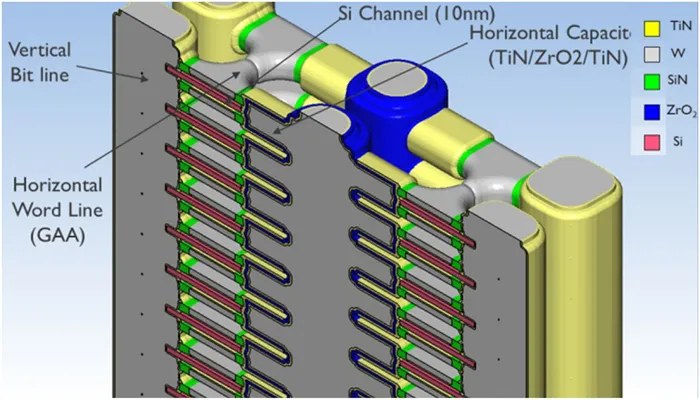

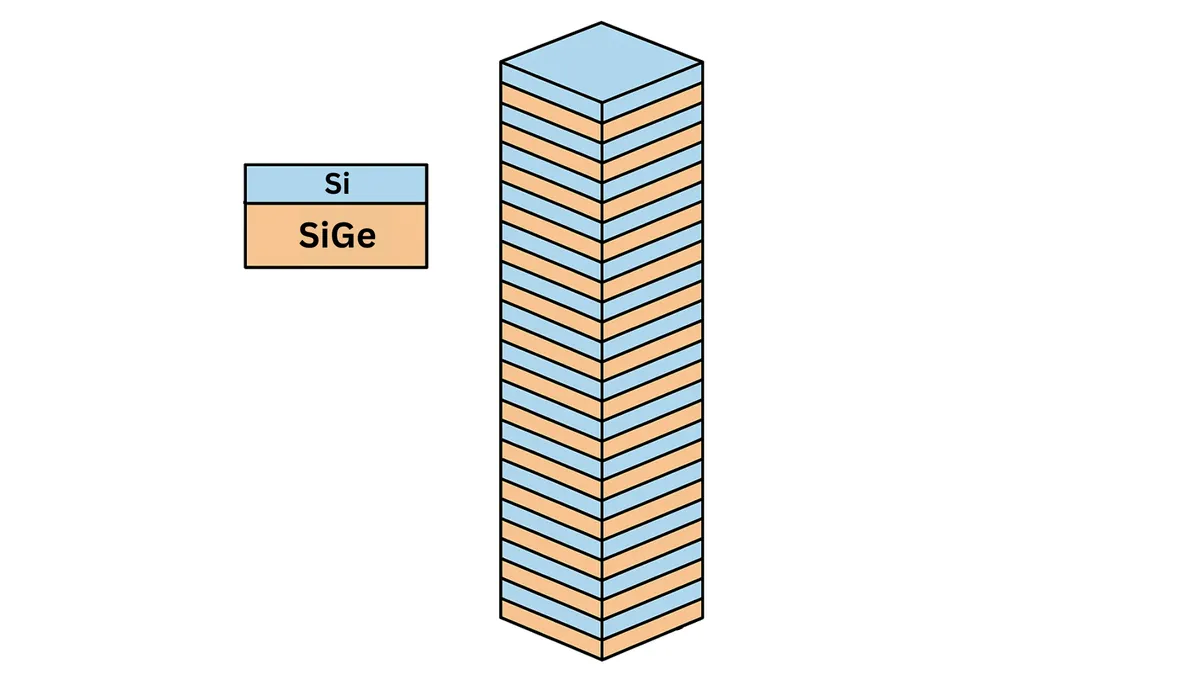

วงการเซมิคอนดักเตอร์กำลังใกล้ถึงการเปลี่ยนแปลงครั้งใหญ่ หลังทีมนักวิจัยจาก imec และ Ghent University สามารถสร้าง “สแต็กชั้นวัสดุ” ได้มากถึง 120 ชั้น โดยใช้ซิลิคอน (Si) และซิลิคอน-เจอร์เมเนียม (SiGe) สลับกันบนเวเฟอร์ขนาด 300 มม. ซึ่งเป็นก้าวสำคัญในการพัฒนา 3D DRAM หรือหน่วยความจำแบบสามมิติที่หลายค่ายผู้ผลิตกำลังเล็งเป็นอนาคตของ DRAM

ถ้าลองจินตนาการง่าย ๆ การสร้างชั้นเหล่านี้ก็เหมือนการสร้างตึกสูงที่มีร้อยชั้น ทุกชั้นต้องตรงและมั่นคง หากชั้นใดชั้นหนึ่งเอียงหรือบิดเบี้ยว ก็จะทำให้ตึกทั้งหลังพังได้ทันที ซึ่งในระดับนาโนเมตร ปัญหานี้ยิ่งทวีความซับซ้อน

ปัญหาที่ต้องฝ่าฟัน: Lattice Mismatch

หัวใจของความยากอยู่ที่ lattice mismatch หรือความต่างระหว่างโครงสร้างผลึกของซิลิคอนกับซิลิคอน-เจอร์เมเนียม แต่ละวัสดุมีระยะห่างอะตอมไม่เท่ากัน เมื่อนำมาซ้อนทับกันชั้นแล้วชั้นเล่า วัสดุเหล่านี้จะพยายามดึงหรือกดกันจนเกิดแรงเครียด (strain) และทำให้โครงสร้างบิดเบี้ยว

ผลลัพธ์คือเกิด misfit dislocation หรือจุดบกพร่องเล็ก ๆ ที่สามารถทำลายประสิทธิภาพของ DRAM ได้ทันที

ทีมวิจัยแก้ปัญหานี้ด้วยการปรับสัดส่วน เจอร์เมเนียม (Ge) ให้เหมาะสมในแต่ละชั้น และทดลองเติม คาร์บอน (C) เข้าไปเล็กน้อย ซึ่งทำหน้าที่คล้ายกาวที่ช่วยผ่อนแรงตึง นอกจากนี้ยังควบคุมอุณหภูมิให้สม่ำเสมอตลอดกระบวนการ เพื่อไม่ให้เกิด “จุดร้อน” หรือ “จุดเย็น” ที่จะทำให้ชั้นวัสดุเติบโตไม่เท่ากัน

เทคนิคการสร้าง: Epitaxial Deposition

กระบวนการนี้ใช้เทคนิค epitaxial deposition ซึ่งเปรียบเหมือน “การเพ้นท์ด้วยแก๊ส” โดยอาศัยก๊าซ Silane และ Germane มาสลายตัวบนผิวเวเฟอร์ แล้วสร้างชั้นซิลิคอนและ SiGe ขึ้นทีละชั้น ความหนาของแต่ละชั้นมีระดับเพียงไม่กี่นาโนเมตร

ความท้าทายคือ ต้องควบคุมทั้งความหนา องค์ประกอบ และความสม่ำเสมออย่างแม่นยำ เพราะความผิดพลาดเพียงเล็กน้อยในชั้นแรก ๆ จะสะสมเป็นความบิดเบี้ยวมหาศาลเมื่อสแต็กสูงขึ้นถึงหลักร้อยชั้น

ทำไมต้อง 3D DRAM?

หน่วยความจำ DRAM แบบดั้งเดิมออกแบบในแนวราบ ทำให้ความหนาแน่นจำกัดไม่สามารถเพิ่มจำนวนเซลล์ได้มากนักโดยไม่เพิ่มขนาดชิป การเปลี่ยนมาใช้ โครงสร้างแนวตั้ง (3D) จะทำให้สามารถบรรจุเซลล์หน่วยความจำได้มากขึ้นในพื้นที่เท่าเดิม

การที่ทีมสามารถสร้างได้ถึง 120 ชั้น แสดงให้เห็นว่า “การขยายแนวตั้ง” หรือ vertical scaling ของ DRAM เป็นไปได้จริง ซึ่งจะช่วยเพิ่มความจุของชิปโดยไม่ต้องเพิ่มพื้นที่หน้าตัดของเวเฟอร์

ผลกระทบต่อวงการชิป

ความสำเร็จนี้ไม่ได้จำกัดอยู่แค่ DRAM เท่านั้น แต่ยังเป็นพื้นฐานสำคัญสำหรับเทคโนโลยีชิปยุคใหม่ เช่น

- 3D Transistor และ Stacked Logic: การสร้างทรานซิสเตอร์และวงจรซ้อนชั้นที่มีความหนาแน่นสูง

- Quantum Computing: โครงสร้างชั้นที่แม่นยำระดับอะตอมสามารถใช้สร้าง Qubit ที่เสถียรขึ้น

- GAAFET และ CFET: ทรานซิสเตอร์แบบใหม่ที่ต้องการการควบคุมคุณสมบัติวัสดุอย่างละเอียด

ยักษ์ใหญ่ในวงการอย่าง Samsung เองก็มีการวางแผนพัฒนาเทคโนโลยีนี้อย่างจริงจัง และตั้งศูนย์วิจัยเฉพาะด้านขึ้นมาแล้ว

มองไปข้างหน้า

แม้ว่าการสร้างสแต็ก 120 ชั้นจะยังเป็นระดับห้องแล็บ แต่ถือเป็นก้าวสำคัญที่พิสูจน์แล้วว่าการพัฒนา 3D DRAM ไม่ใช่เรื่องเพ้อฝันอีกต่อไป ในอนาคตเราจะได้เห็นชิปหน่วยความจำที่มี ความหนาแน่นสูงขึ้นหลายเท่า แต่ใช้พื้นที่และพลังงานน้อยลง

นี่คืออีกหนึ่งหมุดหมายที่แสดงให้เห็นว่า วงการเซมิคอนดักเตอร์กำลังเข้าสู่ยุคใหม่ ที่ไม่ใช่เพียงการทำให้ทรานซิสเตอร์เล็กลง แต่เป็นการออกแบบสถาปัตยกรรมในมิติที่สาม เพื่อสร้าง ความหนาแน่น ความเร็ว และความเสถียร ที่มากกว่าเดิม

สรุป

การวิจัยครั้งนี้เป็นเหมือนการ “สร้างตึกระฟ้าในขนาดนาโนเมตร” ที่เต็มไปด้วยความท้าทายทางฟิสิกส์และวัสดุศาสตร์ แต่หากเดินหน้าต่อไปได้สำเร็จ ก็จะเปลี่ยนโลกของหน่วยความจำและชิปประมวลผลไปอย่างสิ้นเชิง

3D DRAM ไม่ได้เป็นเพียงแนวคิดอีกต่อไป แต่มันกำลังกลายเป็นจริง และอาจเป็นหัวใจของคอมพิวเตอร์ยุคถัดไป

ที่มา: tomshardware