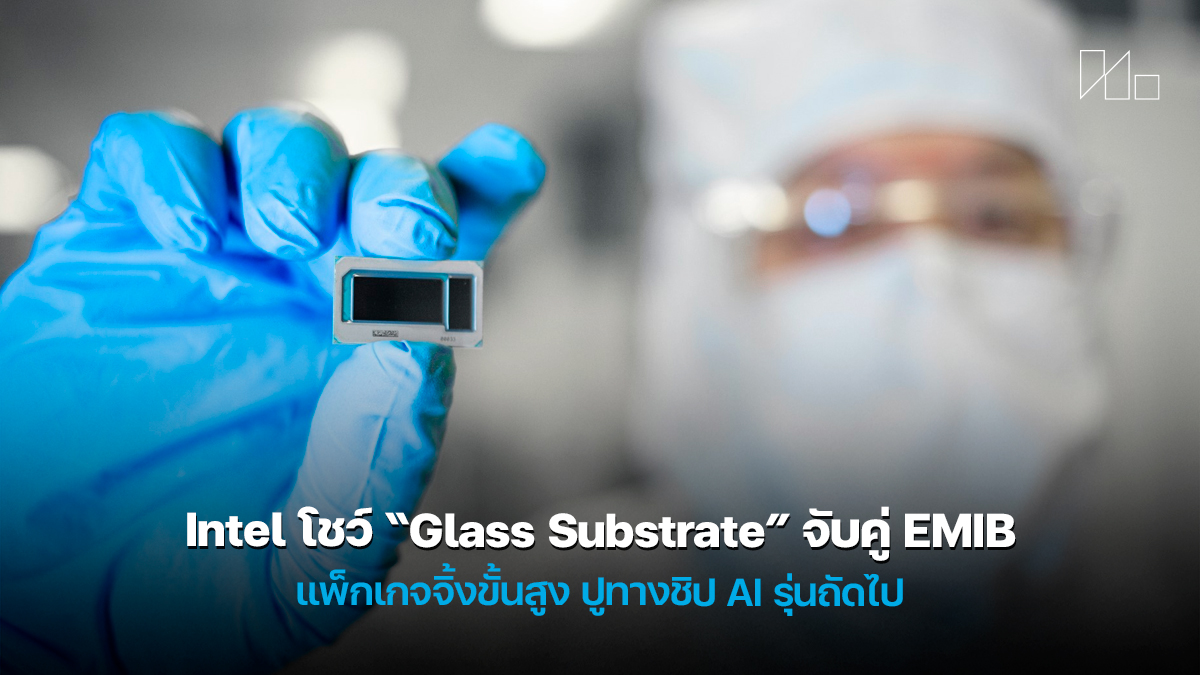

ทำไม “Glass Substrate” ถึงเป็นประเด็นใหญ่ของชิปยุค AI

ช่วงหลังมานี้ “แพ็กเกจจิ้ง” กลายเป็นหัวใจของการพัฒนาชิปพอ ๆ กับการแข่งขันเรื่องกระบวนการผลิต เพราะชิป AI/HPC รุ่นใหม่ไม่ได้พึ่งการทำ die เดียวให้ใหญ่ขึ้นอย่างเดียว แต่พึ่ง “การรวมหลาย die หรือหลาย chiplet” ให้ทำงานร่วมกันในแพ็กเกจเดียวได้แน่นขึ้น เร็วขึ้น และเสถียรขึ้น

ในงาน NEPCON Japan 2026 (จัดช่วงวันที่ 21–23 มกราคม 2026) Intel Foundry นำเสนอแนวทางที่น่าจับตา ด้วยการโชว์แพ็กเกจต้นแบบที่ผสาน EMIB เข้ากับ Glass Substrate โดยวางภาพการใช้งานไปที่กลุ่ม data center และงาน AI accelerator ชัดเจน

EMIB คืออะไร ทำหน้าที่ตรงไหนในแพ็กเกจหลายชิปเล็ต

EMIB (Embedded Multi-die Interconnect Bridge) คือเทคโนโลยีเชื่อมต่อแบบ 2.5D ของ Intel ที่ใช้ “สะพานซิลิคอนขนาดเล็ก” ฝังอยู่ใน substrate เฉพาะจุด เพื่อเชื่อม die หลายตัวให้คุยกันได้ด้วยแบนด์วิดท์สูง

ถ้าพูดให้เข้าใจง่าย: แทนที่จะต้องใช้แผ่น interposer ซิลิคอนขนาดใหญ่ทั้งผืน EMIB จะใช้ “สะพาน” เฉพาะจุดที่ต้องเชื่อมจริง ๆ ทำให้สถาปัตยกรรมแบบหลายชิปเล็ตออกแบบได้ยืดหยุ่นขึ้น และคุมความซับซ้อนของแพ็กเกจได้ในบางแนวทาง

ในโลกของ AI/HPC ที่ต้องการรวม compute tile หลายก้อนเข้าด้วยกัน การมีระบบเชื่อมต่อภายในแพ็กเกจที่หน่วงต่ำและทำได้หนาแน่น จึงเป็นตัวแปรสำคัญมาก

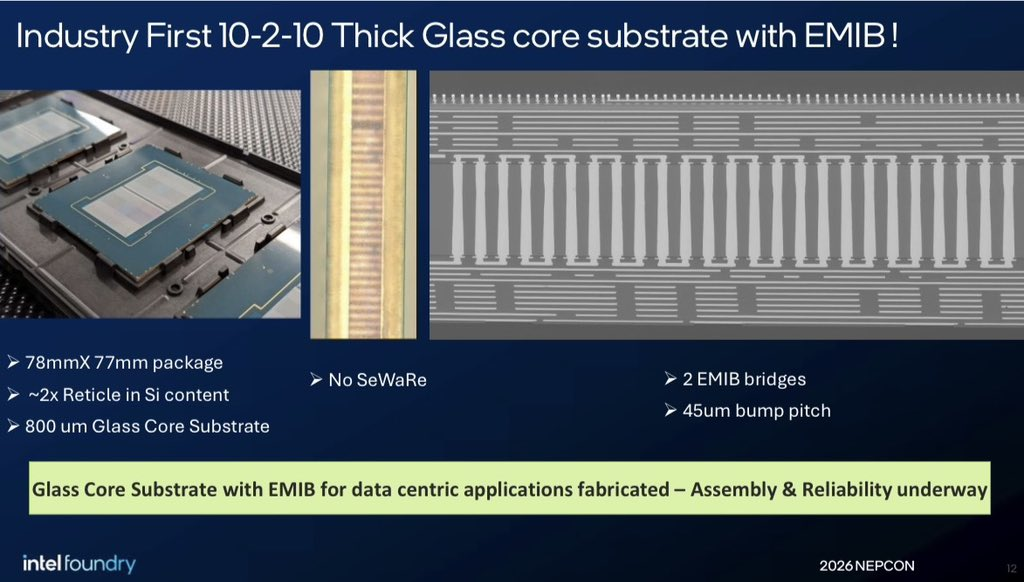

ไฮไลต์ที่ Intel โชว์: EMIB + Glass Substrate แบบ “Thick Core” สำหรับงานระดับเซิร์ฟเวอร์

สิ่งที่ทำให้ข่าวนี้มีน้ำหนัก คือ Intel ไม่ได้พูดเรื่อง Glass Substrate แบบแนวคิดกว้าง ๆ แต่โชว์ “ตัวอย่างเชิงโครงสร้าง” ที่จับคู่กับ EMIB ให้เห็นรูปแบบแพ็กเกจชัดเจน โดยรายงานระบุว่าเป็นแนวทาง “Thick Core” glass substrate และชี้เป้าไปที่งาน data center

รายละเอียดสำคัญที่ถูกยกมา ได้แก่

- ขนาดแพ็กเกจ 78 × 77 มม. ซึ่งเป็นแพ็กเกจขนาดใหญ่ เหมาะกับสินค้ากลุ่มเซิร์ฟเวอร์และ AI accelerator

- แนวคิดการสเกลแพ็กเกจไปถึงระดับ “2× reticle size” (อธิบายแบบเข้าใจง่ายคือ เป็นการต่อยอดให้ “แพ็กเกจ” รองรับการรวมหลาย die ได้ใหญ่กว่าขนาด die เดี่ยวที่ติดข้อจำกัดทางลิโทกราฟี)

- โครงสร้างชั้นวัสดุแบบ 10-2-10 stack-up

- ด้านบนมีชั้น RDL (Redistribution Layer) 10 ชั้น

- ตรงกลางเป็น glass core 2 ชั้น

- ด้านล่างเป็นชั้น build-up อีก 10 ชั้น

- มีการใส่ EMIB bridge 2 ตัว ภายในแพ็กเกจ เพื่อเชื่อม die หลายตัวเข้าหากัน

ทั้งหมดนี้สะท้อนภาพว่า Intel กำลังพยายามทำ “แพ็กเกจใหญ่” ที่ยังเดินสัญญาณได้แน่น และรองรับการต่อชิปเล็ตหลายตัวในแพ็กเกจเดียวให้ได้จริงในอนาคต

ทำไมต้องเป็น Glass Substrate: จุดที่ substrate แบบเดิมเริ่มชนเพดาน

ปกติ substrate จำนวนมากในอุตสาหกรรมใช้วัสดุแบบ organic (แนวเรซิน/อินทรีย์) ซึ่งทำงานได้ดีและคุ้มค่าในระดับหนึ่ง แต่เมื่อแพ็กเกจ “ใหญ่ขึ้น” และ “เดินสายถี่ขึ้น” จะเริ่มเจอปัญหาสำคัญ เช่น

- การบิดงอของแพ็กเกจ (warpage) เมื่อขนาดใหญ่และชั้นวัสดุหนาแน่น

- ความไม่สอดคล้องของการขยายตัวตามความร้อน ระหว่างวัสดุหลายชนิด (ยิ่งชิปทำงานหนัก ยิ่งเกิดความต่าง)

- ข้อจำกัดด้านความละเอียดของการเดินสัญญาณ เมื่ออยากอัดความหนาแน่นของเส้นทางสัญญาณให้สูงขึ้นอีก

จุดแข็งของ Glass Substrate คือคุณสมบัติเชิงกลและเชิงมิติที่ “นิ่ง” มากขึ้น เหมาะกับการทำแพ็กเกจขนาดใหญ่ที่ต้องคุมความแบน ความเสถียร และความหนาแน่นของการเดินสายให้สูงในระดับ data center

ในบริบทของ AI/HPC ที่ต้องการรวมชิปเล็ตจำนวนมากในแพ็กเกจเดียว การลดความเครียดเชิงกลและการคุมความแม่นยำของการเดินสัญญาณ คือสิ่งที่ช่วยให้สเกล “ซูเปอร์แพ็กเกจ” ไปต่อได้จริง ไม่ใช่ติดเพดานด้านการประกอบหรือความเสถียรของแพ็กเกจ

มุมอุตสาหกรรม: ทำไมการขยับของ Intel รอบนี้น่าจับตา

ข่าวนี้ยังเชื่อมกับภาพใหญ่ของตลาด advanced packaging ด้วย เพราะช่วงหลังอุตสาหกรรมกำลังเผชิญ “คอขวด” ด้านกำลังการผลิตแพ็กเกจระดับสูง (โดยเฉพาะงานที่เกี่ยวกับชิป AI) ทำให้ผู้เล่นจำนวนมากมองหาแนวทางเชื่อมต่อ die และขยายแพ็กเกจที่ทำได้จริงในเชิงอุตสาหกรรม

สำหรับ Intel การโชว์ EMIB + Glass Substrate ในงานอุตสาหกรรมจึงตีความได้ว่า บริษัทกำลังพยายามย้ำบทบาท “แพ็กเกจจิ้งขั้นสูง” ในฐานะโอกาสของ Intel Foundry และเป็นหนึ่งในพื้นที่ที่สามารถสร้างความแตกต่างได้ในยุคชิป AI ที่โตจากการรวมชิปเล็ตและระบบหน่วยความจำมากขึ้นเรื่อย ๆ

สรุป: Glass Substrate + EMIB คือหมากสำคัญของชิป AI รุ่นถัดไป

การนำ Glass Substrate มาจับคู่กับ EMIB ในตัวอย่างแพ็กเกจระดับใหญ่ เป็นสัญญาณว่า Intel ยังเดินหน้ากับแนวคิดนี้อย่างจริงจัง เพื่อรองรับยุคที่ชิป AI/HPC ต้อง “รวมหลาย die หลาย chiplet” ในแพ็กเกจเดียวมากขึ้น

ถ้าแนวทางนี้สเกลไปสู่การใช้งานจริงได้ตามแผน ก็มีโอกาสที่ advanced packaging จะเป็นหนึ่งในปัจจัยชี้ขาดของการแข่งขันชิป AI รุ่นถัดไป ไม่แพ้การแข่งขันเรื่อง node หรือสถาปัตยกรรมภายในตัว die

ที่มา: wccftech